先週末~金曜作った12bit in 12bit outのsinテブルを使い、土日に16時間ほどかけて純正律のオルガンを実装しました。前から作りたかったんですよ。

が、色々問題があって、完成に至りませんでした。

完成しなかったので完成品のプロジェクトは出せないんですが、問題点リストは需要があるかもなので、そちらをupします。

■■MAX10はROM推測できないの?

ALTERAのデバイスは、ピュアHDLで書いても(IPを使わなくても)ROMを実装することができます。(XilinxでもMicroSemiでもLatticeでも多分できますが。)

具体的には、以下の

「6. 推奨される HDL コーディング構文」6-24

https://www.altera.co.jp/ja_JP/pdfs/literature/hb/qts/qts_qii51007_j.pdf

の記述方法でROM推測してくれて、M9Kに展開してくれる筈なんですが、

MAX10 + Quartus Prime v15.1の組み合わせでは旨くゆきませんでした。

入力/出力両方にDFFを入れてみたんですが、それもダメ。

Cyclone I、CycloneVに、同じコードを入れてみましたが、こちらは推測してくれました。

困る。何が困るかというと、IPで設計しちゃうと、他のベンダー移植に労力がかかるし、simも大変になるし、sim実行に時間もかかります。

>>>解決 --160104mo追記

Device オプションで DeviceAndPinOptions->ConfigurationMode:で

~MemoryInitializationを選べば行けるみたいです。

が、MAX10は、FやA classのdual configできるデバイスでないとダメみたいですね?(容量のせいなのか、configデバイスのせいなのかは不明)

■14bit4入力加算は78MHz

BeMicroMAX10搭載の10M08DAF484C8GEは、4入力s13bit加算に、78MHzかかりました。

しかたないので、2入力づつ1段叩いたら150MHz以上になりました。

192MHz動作するつもりでしたが、144MHzに妥協することに。

もう少し気にする必要があったみたいですね。

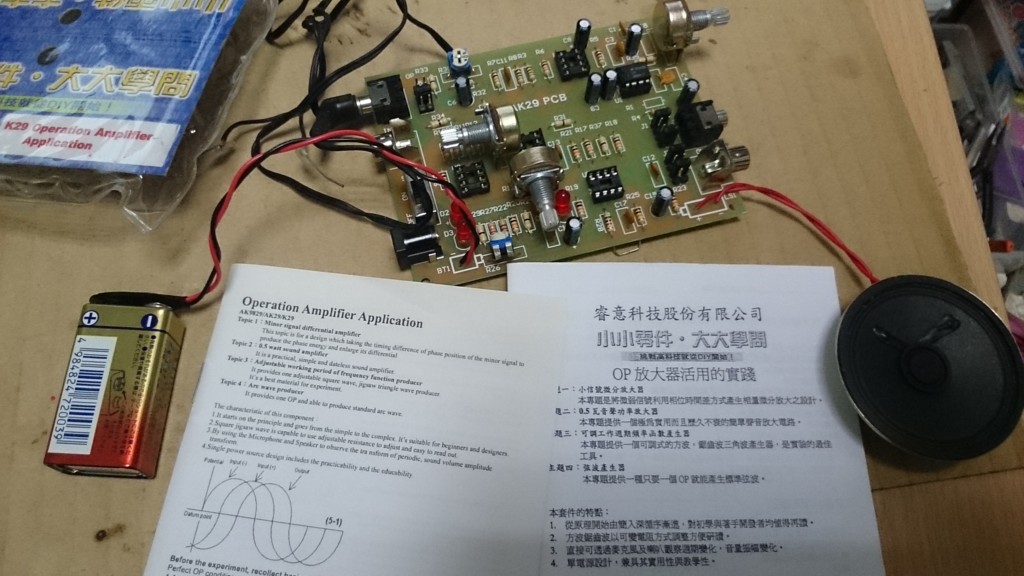

■サウンダーは効率悪いし歪むよ

音出力は3.3VI/Oを逆相2ポート使って、サウンダー(100円ショップの盗難ブザーの圧電素子)を鳴らす予定でしたが、フルスイングでも、300Hzの正弦波はなんとか聞こえるレベル。

8和音とか言うと、1つの音の波高値はフルスイングの1/8になるので、パワーは-18dB(1/64)。結構HiFi?

おまけに、スプリアスがバリバリでるので、音質どころか、和音なんて言えないレベルでした。FFTの波高値で1/3くらいあるスプリアス。少なくともダイナミックスピーカーが必要なレベルなんですが、設計めんどっちーです。

多分100円ショップで探せば32Ω品があるので、それを8パラドライブすれば、聞こえるレベルにはなると思うんですが...

■和音用分周回路の比率計算間違い。

任意周波数のシンセサイザーには、最近はやりのDDSみたいに、任意ステップのカウンタ(ステップ幅を周波数に比例させて大きくする)方法と

ステップは1で、1ステップ上がる時間を周波数の逆数に比例させるカウンタを使う方法がるわけです。

・ステップを変える方法の弱点

ステップ可変の方法は、システムクロック周波数を厳密に考える必要がなく、かなり自由な設計が出来る代わりに、システムクロック幅のジッターを持つ宿命にあります。

・周期(時間間隔)を変える方法の弱点

逆に時間周期を変える方法は、作りたい周波数の波長の最小公倍数をマスタクロックにして、マスタクロックとの公倍数ごとに1カウントアップするような方法を取ります。

普通、マスタクロックの周波数がものすごく大きくなって、計算も大変なので、拒否られる方向です。

でも、ジッタはシステムクロックのスキュー分にとどまります。

この表は純正律の各音の周波数(f)と周期(T)の比を通分したものです。

周波数は24、周期は180が分母になります。純正律は波長の比が単純なのが売りで

そのためにキレイな響きを発することができるのですが、それでも最小公約数が180にもなります。

これを元に、マスタクロックを計算して、48MHzでイイはず、だったんですが、

実装してオシロで周波数を測ってはじめて気が付きました。分母の108いらなかったのね。108だし。

正しくは

fCKE=440x2^4x108x4096=3.114GHz

マスタークロック3.114GHzじゃん。というわけでした。

とりあえず、マスタークロックを144MHzにすればC7が200Hz前後になるため、今日は、この音を聴いて終わりということに。

残念!